# University of Castilla–La Mancha

# A publication of the Computing Systems Department

## An Alternative for Building High-Radix Switches: Formalization and Configuration Methodology\*

by

J.A. Villar, F.J. Andújar, J.L. Sánchez, F.J. Alfaro, J. Duato

Technical Report #DIAB-11-02-1 February 2011

(\*) This work was supported by the Spanish MEC and MICINN as well as European Comission FEDER funds, under Grants "Consolider Ingenio-2010 CSD2006-00046" and "TIN2009-14475-C04", respectively; it was also partly supported by Junta de Comunidades de Castilla-La Mancha under grants "PCC08-0078-9856" and "POII10-0289-3724".

DEPARTAMENTO DE SISTEMAS INFORMÁTICOS

ESCUELA SUPERIOR DE INGENIERÍA INFORMÁTICA

UNIVERSIDAD DE CASTILLA-LA MANCHA

CAMPUS UNIVERSITARIO s/n

02071, ALBACETE, ESPAÑA

Tlf. +34.967.599200, Fax +34.967.599224

# An Alternative for Building High-Radix Switches: Formalization and Configuration Methodology

Juan A. Villar, Francisco J. Andújar Instituto de Investigación en Informática Campus Universitario s/n 02071 – Albacete, España {juanan,fandujar}@dsi.uclm.es

Francisco J. Alfaro, José L. Sánchez Departamento de Sistemas Informáticos Escuela Superior de Ingeniería Informática 02071 – Albacete, España {falfaro, jsanchez}@dsi.uclm.es

José Duato

Dpto. de Ingeniería de Sistemas y Computadores

Camino de Vera, s/n

Universidad Politécnica de Valencia

46022 - Valencia, España

jduato@gap.upv.es

February 7, 2011

# Contents

| 1            | Intr                     | roducti  | on                                                                                            | 7  |

|--------------|--------------------------|----------|-----------------------------------------------------------------------------------------------|----|

| <b>2</b>     | Hig                      | h-Radi   | x Switches by Combining Low-Radix Switches                                                    | 9  |

|              | 2.1                      | Combi    | ned Switches                                                                                  | 9  |

|              | 2.2                      | Combi    | ned Switches Configuration Methodology                                                        | 11 |

|              | 2.3                      | Study    | Conditions                                                                                    | 12 |

| 3            | Not                      | tation   |                                                                                               | 12 |

| 4            | Twi                      | in swite | ches                                                                                          | 13 |

|              | 4.1                      | Interna  | al connections of Twin switches                                                               | 18 |

| 5            | Applying the Methodology |          |                                                                                               |    |

|              | 5.1                      | Netwo    | rks paths analysis                                                                            | 21 |

|              |                          | 5.1.1    | Reachable nodes from a BMIN switch considering the network topology                           | 22 |

|              |                          | 5.1.2    | Reachable nodes from a BMIN switch considering the network topology and the routing algorithm | 25 |

|              |                          | 5.1.3    | Ascending phase of the paths                                                                  | 31 |

|              |                          | 5.1.4    | Turnaround phase of the paths                                                                 | 32 |

|              |                          | 5.1.5    | Descending phase of the paths                                                                 | 32 |

|              | 5.2                      | Switch   | Classification                                                                                | 34 |

|              | 5.3                      | Switch   | Configuration                                                                                 | 35 |

|              |                          | 5.3.1    | Type $va$ configuration of switch                                                             | 36 |

|              |                          | 5.3.2    | Type $vb$ configuration of switch                                                             | 46 |

|              |                          | 5.3.3    | Configuration of switch                                                                       | 46 |

| 6            | Hig                      | h-radix  | Switches                                                                                      | 47 |

| $\mathbf{A}$ | Mu                       | ltistage | e Interconnection Networks                                                                    | 52 |

| A.1 | Multistage interconnection networks | 52 |

|-----|-------------------------------------|----|

| A.2 | Preliminary definitions             | 53 |

|     | A.2.1 Notation                      | 54 |

| A.3 | Connection pattern                  | 55 |

| A.4 | Unidirectional MINs                 | 56 |

|     | A.4.1 Self–routing algorithm        | 57 |

| A.5 | Bidirectional MINs                  | 58 |

|     | A.5.1 Turnaround–routing algorithm  | 60 |

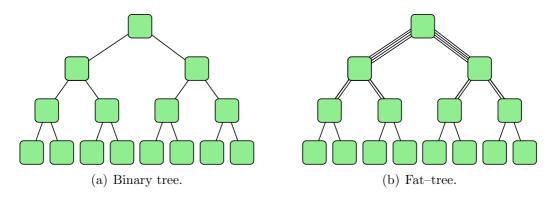

| A.6 | Fat-tree topology                   | 61 |

|     | A.6.1 $k$ -ary $n$ -tree topology   | 62 |

| A.7 | Load-balanced routing algorithm     | 63 |

|     | A.7.1 DESTRO routing algorithm      | 65 |

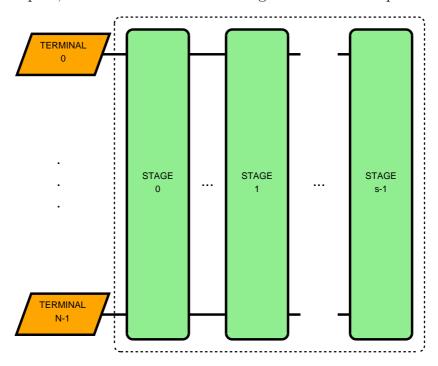

### 1 Introduction

Interconnection networks are a key component for a wide range of multiprocessor systems, ranging from large supercomputers to multicore chips. High performance networks are essential in these systems, where high reliability in communications, high information transfer rates and very low latencies are critical. Often, the interconnection network is the subsystem that a more custom design requires. For instance, Tianhe-1A supercomputer [SS10], number one in the November 2010 Top500 list, is composed of standard Intel® and NVIDIA® processors and a fancy new interconnection network. This custom interconnect design removes the interconnect bottleneck and significantly contributes to the high global performance of Tianhe-1A.

Interconnection network design is determined by the available technology. Recent advances on the technology have substantially improved the performance of the basic network components: links and switches. The latter are responsible for most of the interconnection network performance, and so they are the subject of major research. One of the main parameters characterizing network switches is the number of ports, which has a strong influence on cost, consumption and performance in the whole system.

Given a multiprocessor system with a large number of connected elements, increasing the number of switch ports results in a decrease in the number of switches and network links. As the cost of the network is proportional to the number of switches, it is clear that cost decreases by using switches with higher number of ports. Moreover, total consumption of the network is also considerably reduced as it is directly proportional to the number of switches in the network.

Regarding performance, in terms of latency, for example, it is clear that the use of switches with more ports involves a reduction in the average time to transfer data over the network. In particular, using fewer switches to connect the same number of elements reduces the number of hops and the number of possible packet collisions in the network, and thus the time to reach their destinations. Furthermore, having less switches, the total processing time of the packets in the switches along their paths is also reduced.

Thus, the design of switches with a high number of ports is an attractive option to improve the performance and reduce the cost of the interconnection network, specially for large multiprocessor systems. However, there are some problems to design such switches. One of them is related to the complexity of the switch logic. The switch becomes more complex as radix increases, taking up to a significant percentage of total system power [WPM03]. The balance between cost and efficiency is not easy to work through, requiring a deep study regarding this trade-off. On the one hand, the size of some switch structures grows quadratically with the number of ports. That is the case of, for example, the aggregate buffer requirements as identified in [GAG<sup>+</sup>03], or the schedulers as stated in [MAM<sup>+</sup>05]. Moreover, traditional flow control policies are also affected by switch radix in two aspects [MG07]: the round trip time drastically increases, and the memories for storing flow control credits are linearly dependent on

8 1 INTRODUCTION

the round trip time. On the other hand, pin count will slowly increase next decade, according to the ITRS [fSI10], and therefore switch ports number will slightly increase. Moreover, there are difficulties to apply some improvement techniques when the number of ports is high. For instance, Virtual Output Queuing (VOQ) implementation becomes unfeasible in practice for switches with large number of ports. To overcome these problems, different solutions have been proposed, but actually, they are postponing the problem for coming switch generations.

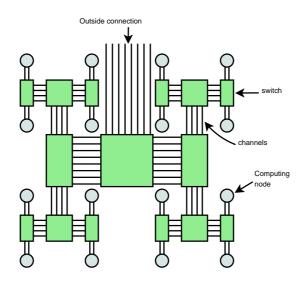

In any case, switch size constraints are mainly determined by the current integration scale and package pin count. To go beyond the integration scale bounds, an alternative solution for building high-radix switches is the combination of several low-radix switches. This solution has the advantage of obtaining higher number of ports. Moreover, some difficulties mentioned above lose importance.

The main idea is to implement n-port switches from several smaller m-port switches. For instance, a n-port switch consisting of two identical m-port switches (n/2 < m < n) can internally interconnect each other using m - n/2 ports, using the remaining ports for external connections. Note that this strategy will remain valid as integration scale keeps evolving.

An important consequence of this strategy for building larger switches is that the resulting switch will no longer be homogeneous. Switch performance will vary depending on the internal configuration. The internal switches interconnection can become a potential bottleneck if they have to support most of the traffic handled in the switch. Therefore, it is essential to minimize the impact of this bottleneck, otherwise the latency on the network will be increased. Thus, the switch-level connection pattern becomes an important design decision in the construction of this kind of switches. An arbitrary pattern may produce a significant performance degradation. Consequently, it is necessary to determine the most convenient pattern in order to obtain the best switch performance.

In this paper, we present a formalization of this kind of high-radix switches and propose a methodology for configuring them in an optimal manner when they are used to build large switch—based interconnection networks. To show how this methodology works, it is applied to a particular interconnection network.

The report is organized as follows: Section 2 describes the *combined switches*, and in Section 3 we introduce the notation used later. Section 4 formally defines and characterizes the *twin switches*. In Section 5, we propose our methodology for searching the optimal configuration of *twin switches*, and show how it works in a particular case. Section 6 gives a brief review to existing proposals on high-radix switches. Additionally, in the A we have included basic concepts on multistage interconnection networks.

<sup>&</sup>lt;sup>1</sup>We distinguish between network-level connection pattern and switch-level connection pattern. The former is the traditional interconnection pattern connecting switch-based networks (e.g. butterfly permutation in multistage interconnection networks); and the latter refers to how every high-radix switch ports are mapped to the ports of the internal switches.

# 2 High-Radix Switches by Combining Low-Radix Switches

As mentioned above, it is possible to build high-radix switches by combining several low-radix switches. This strategy makes possible to eventually overtake integration technology and dramatically shorten the time-to-market. Note that this will remain valid as integration technology continues evolving.

This strategy opens a series of new issues that must be addressed so that it would be implemented in an efficient manner. In this section, we define the combined switches and briefly overview the issues characterizing them. Then in the next sections, we formally analyze them in depth.

#### 2.1 Combined Switches

In this section we define the combined switches giving a general definition. Then we turn our attention to a particular subclass of this kind of switches, which will be used in order to show the characteristics and evaluate the performance of combined switches as a high-radix switch alternative.

**Definition 1.1** A Combined switch, or simply C-switch, is a switch formed by several smaller interconnected switches (internal switches). The ports being offered by a C-switch are obtained from free ports of its internal switches after they are interconnected.

This is a general definition because it does not specify either the number of internal switches or their radix. Therefore any switch obtained by combining other lower switches is included in this category. However, there exist some difficulties to build C-switches having many internal switches and a high heterogeneity degree.

In order to keep low the internal latency, a full-connected subnetwork interconnecting all the internal switches is preferred. As the number of internal switches increases, the number of ports dedicated to subnetwork connections grows as fast as the number of ports devoted to external communications decreases, so this way of building high-radix switches would lose interest. Therefore, it seems reasonable that the number of internal switches may not be too large.

On the other hand, a simpler C-switch internal design can be achieved if all the internal switches are equal. Although this aspect is not as restrictive as the number of internal switches, it would be also recommendable that all the internal switches have the same radix.

An interesting case is that where C-switches are built from only two identical internal switches. This subclass of C-switches still offers an important increase in the

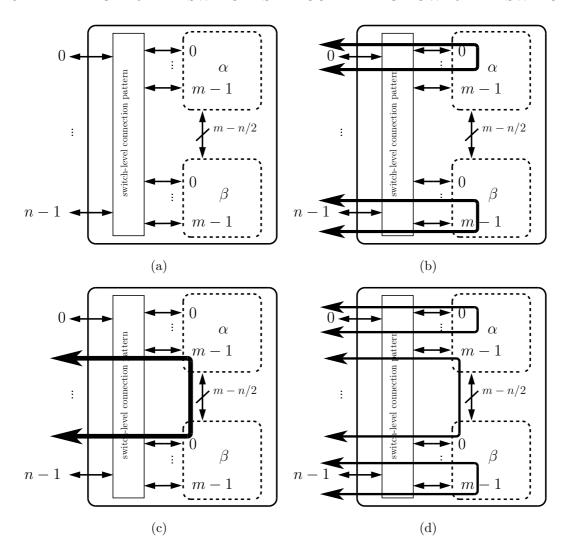

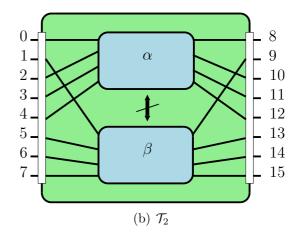

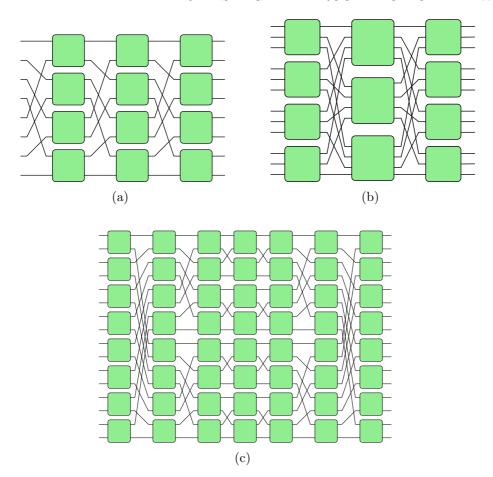

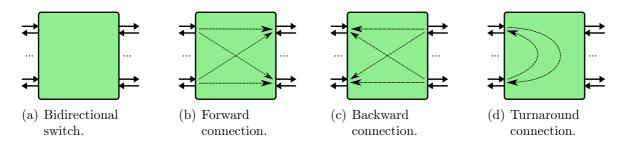

Figure 1: (a) Basic block diagram of a T-switch and several cases: (b) Optimal, (c) Bad, and (d) General.

number of ports while the interconnection between the two internal switches is the simplest one.

**Definition 1.2** A Twin switch, or simply T-switch, is a switch formed by two identical smaller interconnected switches. The ports being offered by a T-switch are obtained from free ports of its two internal switches after they are interconnected.

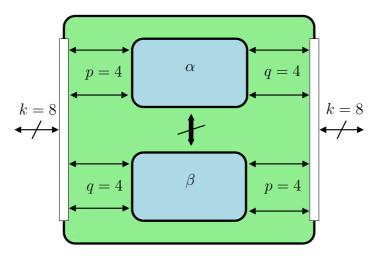

Considering that the two internal switches and the T-switch have radixes m and n, respectively, Figure 1(a) shows a basic diagram of a T-switch, where internal switches are denoted as  $\alpha$  and  $\beta$ . Although T-switches seem to be simple, there are significant challenges in its design. Two of them stand out especially: (1) to obtain the appropriate switch-level connection pattern of internal subnetwork, (2) to determine the adequate number of ports used to interconnect switches  $\alpha$  and  $\beta$ .

Switch-level connection pattern has an important influence on packet latency. Time to cross the T-switch will be minimal when only one internal switch ( $\alpha$  or  $\beta$ ) is

used (Figure 1(b)). The bad case is obtained when both internal switches are used for every path crossing the T-switch (Figure 1(c)). To obtain the best case is not trivial and an in-depth study is required, in which several factors, e.g., network topology, routing and traffic pattern must be considered. From Section 2.2 we show in a formal way how the optimal switch-level connection pattern can be obtained if these factors are considered.

Regarding the second challenge, the number of internal ports must be that which avoids the creation of the internal bottleneck between  $\alpha$  and  $\beta$ . Obviously, the number of internal ports and the switch-level connection pattern have a clear interdependence.

The situations shown in Figure 1(b) and Figure 1(c) are appropriate for illustrating the T-switch design challenges, but a more common situation is that shown in Figure 1(d), where both kinds of cases coexist. In such situations, the main objective in the switch-level connection pattern design of T-switches is to minimize the use of the ports interconnecting the internal switches.

Therefore, since in some cases communication will require the use of both internal switches (i.e. a path passing through a T-switch will use both  $\alpha$  and  $\beta$ ), we have to avoid interconnection between  $\alpha$  and  $\beta$  becomes a bottleneck. Moreover, the adequate number of ports of each internal switch to connect with each other must be determined. It is clear that the greater the number of ports used to interconnect the internal switches the lower the probability of this interconnection becomes a bottleneck. However, as mentioned above, as the number of ports devoted to interconnect  $\alpha$  and  $\beta$  increases the T-switch radix decreases. Note that we are assuming that all the ports provide the same bandwidth (otherwise instead of using the number of ports, the aggregate bandwidth should be used). Consequently, a trade-off between both aspects must be found.

In summary, internal configuration of T-switches, and in general C-switches, becomes a key aspect in the design of this kind of high-radix switches. In the following Section, we present a general methodology to obtain the best configuration of this kind of switches when they are used in large interconnection networks. It is obvious that optimal configuration of a C-switch depends on the conditions under which it is used, that is, network type, topology, routing algorithm, traffic pattern, etc. To show how the methodology works, we apply it to a particular subclass of interconnection network.

## 2.2 Combined Switches Configuration Methodology

Our methodology to determine the optimal switch-level connection pattern of C-switches consists of the following main steps:

1. Network paths analysis. The purpose of this step is to determine the connections required in each C-switch at network level and the amount of times all these connections are used taking into account all the possible paths used by the packets.

12 3 NOTATION

2. Switch classification. Depending on the network characteristics and load conditions, few or many different C-switch configurations could be obtained. In this step, C-switches are grouped according to their connection requirements, and so, several types of C-switch will be distinguished.

As result of the previous phase, it can occur that some of the possible connections in the C-switches support one, or more paths, and however there may be connections that are never established.

In a fat-tree topology, for instance, C-switches in different stages may require different switch-level connection patterns, and the same may even occur with C-switches in the same stage. When a simple traffic pattern and balanced routing algorithm are used, it is likely all the C-switches in the network require the same switch-level connection pattern.

3. Switch configuration. From connection requirements and given the number of internal switches forming the C-switch, this last step consists in finding the optimal configuration for each class of C-switch. That is, we must find the optimal switch-level connection pattern of each class, trying to minimize the use of the interconnection between internal switches.

#### 2.3 Study Conditions

As above mentioned, switch-based interconnection networks cover a wide range of network configurations. To present our formal analysis of the C-switches behavior and how they can be configured in an optimal way, we have chosen a very representative case. On the one hand, we consider T-switches due to the reasons outlined in Section 2.1. On the other hand, and since fat-trees are one of the most common topologies today in the largest supercomputers on the Top500 list, we focus on bidirectional interconnection networks (BMINs).

## 3 Notation

We have assumed the following notation throughout this paper:

- $\bullet$  N is the total number of terminals.

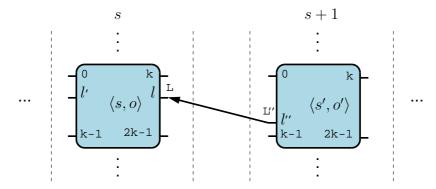

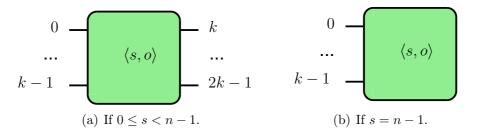

- k is the switch arity, or number of ports that connect to terminals/switches in the previous stage and switches in the next stage (if available). Hence, the total number of ports of a  $k \times k$  switch is 2k. The ports faced to the previous stage are numbered from 0 to k-1, and the ports connected with the switches in the next stage are labeled from k to 2k-1.

- Every switch port has an associated global identifier inside the stage,  $L = l_{n-1} \dots l_0, 0 \le l_i < n$ , apart from the internal identifier inside the switch. Both identifiers are related by the connection pattern between stages.

- n is the total number of stages, where  $n = \log_k N$ .

- h is the terminal identifier  $(0 \le h < N)$ . It consists of a string of n digits  $h_{n-1} \dots h_1 h_0$   $(0 \le h_i < k)$ .  $\mathcal{H}$  is the set whose members are the terminals of the MIN, verifying  $card(\mathcal{H}) = N$ .

- $\langle s, o \rangle$  is a tuple that identifies uniquely a switch, where s refers to the stage  $(0 \le s < n)$ , and  $o = o_{n-2}, \ldots, o_1, o_0$  indicates the position of the switch inside the stage, where  $0 \le o_i < k$  and  $0 \le i < n-1$ .

#### 4 Twin switches

We fully characterize the T-switches by means of the following definitions and propositions.

**Definition 1.3** Let  $\mathcal{U}$  be the set of ports on a  $k \times k$  switch. Hence,

$$\mathcal{U} = \{ i \in \mathbb{N}, \ 0 < i < 2k \}$$

**Definition 1.4** Let  $\mathcal{B}$  be the set of ports on a  $k \times k$  switch connecting to switches from the previous stage (or the input ports in a MIN). Hence,

$$\mathcal{B} = \{ i \in \mathcal{U}, \ 0 < i < k \}$$

**Definition 1.5** Let  $\mathcal{F}$  be the set of ports on a  $k \times k$  switch that connect to switches on the next stage in a MIN network. Hence,

$$\mathcal{F} = \{i \in \mathcal{U}, \ k < i < 2k\}$$

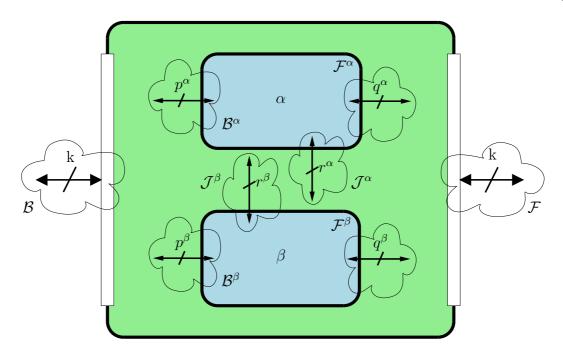

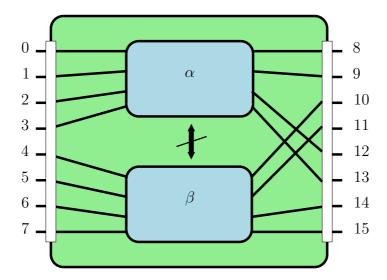

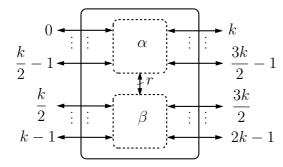

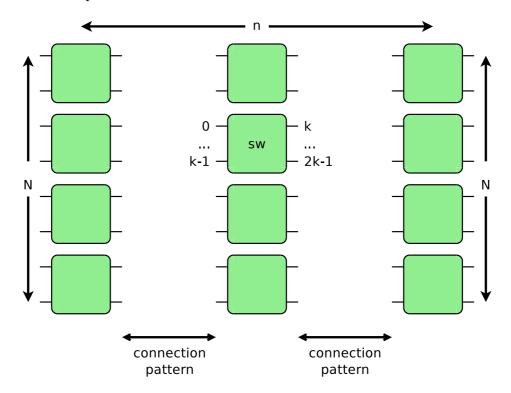

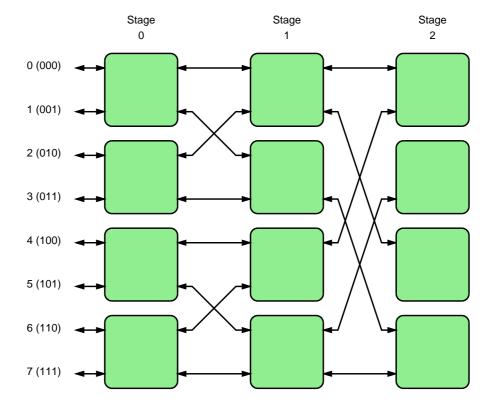

Figure 2 shows the detailed organization of T-switches. From Definitions 1.3, 1.4, and 1.5 it is obvious that  $card(\mathcal{U}) = 2k$  and  $card(\mathcal{B}) = card(\mathcal{F}) = k$ , where card is the cardinality of sets.

Most of the internal switch ports are dedicated for external communications, meanwhile a concrete number of them are responsible for intra communications between internal switches.

$$\mathcal{B} = \mathcal{B}^{\alpha} \cup \mathcal{B}^{\beta}$$

.  $\mathcal{B}^{\alpha} \cap \mathcal{B}^{\beta} = \emptyset$

$$\mathcal{F} = \mathcal{F}^{\alpha} \cup \mathcal{F}^{\beta}, \ \mathcal{F}^{\alpha} \cap \mathcal{F}^{\beta} = \emptyset$$

According to the above, T-switches can be re-defined as follows:

**Definition 1.6** A  $k \times k$  T-switch is a bidirectional switch formed by two identical smaller interconnected switches. the 2k ports being offered by this T-switch are obtained from the k free ports of each internal switch after they are interconnected by r ports.

**Definition 1.7** Let  $\mathcal{P}^i$  be the set of ports on the switch i, where  $i \in \{\alpha, \beta\}$ . Moreover,  $\mathcal{P}^i$  is divided into three disjoint subsets  $\mathcal{J}^i$  to interconnect the internal switches,  $\mathcal{B}^i$ , and  $\mathcal{F}^i$  for the T-switch ports.

In a more formal way:

- $\mathcal{P}^i = \mathcal{J}^i \cup \mathcal{B}^i \cup \mathcal{F}^i$

- $\mathcal{J}^i \neq \emptyset$

- $\mathcal{B}^i \cap \mathcal{F}^i = \emptyset$ ,  $\mathcal{B}^i \cap \mathcal{J}^i = \emptyset$  and  $\mathcal{F}^i \cap \mathcal{J}^i = \emptyset$

According to this, it is clear to derive that:

- $\operatorname{card}(\mathcal{J}^{\alpha}) = \operatorname{card}(\mathcal{J}^{\beta})$

- $\operatorname{card}(\mathcal{P}^{\alpha}) = \operatorname{card}(\mathcal{P}^{\beta})$

**Proposition 1.1** In a T-switch consisting of two internal switches  $\alpha$  and  $\beta$ , it is verified that

$$card(\mathcal{B}^{\alpha}) = card(\mathcal{F}^{\beta})$$

$and card(\mathcal{B}^{\beta}) = card(\mathcal{F}^{\alpha}).$

**Proof:** According to Definition 1.7 we know how the switch ports of  $\alpha$  and  $\beta$  are configured:

$$\mathcal{B} = \mathcal{B}^{\alpha} \cup \mathcal{B}^{\beta} \quad \text{and} \quad \mathcal{B}^{\alpha} \cap \mathcal{B}^{\beta} = \emptyset$$

$$\mathcal{F} = \mathcal{F}^{\alpha} \cup \mathcal{F}^{\beta} \quad \text{and} \quad \mathcal{F}^{\alpha} \cap \mathcal{F}^{\beta} = \emptyset$$

since the sets are disjoint, the expression can be rewritten as

$$card(\mathcal{B}) = card(\mathcal{B}^{\alpha}) + card(\mathcal{B}^{\beta}) = k$$

$card(\mathcal{F}) = card(\mathcal{F}^{\alpha}) + card(\mathcal{F}^{\beta}) = k$

Figure 2: T-switch.

clearing equations

$$card(\mathcal{B}^{\beta}) = k - card(\mathcal{B}^{\alpha})$$

(1)

$$card(\mathcal{F}^{\alpha}) = k - card(\mathcal{F}^{\beta})$$

(2)

and also

$$card(\mathcal{B}^{\alpha}) = k - card(\mathcal{B}^{\beta})$$

(3)

$$card(\mathcal{F}^{\beta}) = k - card(\mathcal{F}^{\alpha})$$

(4)

On the other hand, the Definition 1.7 describes how the switch ports of  $\alpha$  and  $\beta$  are distributed,

$$\mathcal{P}^{\alpha} = \mathcal{J}^{\alpha} \cup \mathcal{B}^{\alpha} \cup \mathcal{F}^{\alpha}$$

$$\mathcal{P}^{\beta} = \mathcal{J}^{\beta} \cup \mathcal{B}^{\beta} \cup \mathcal{F}^{\beta}$$

and also

$$\mathcal{B}^{\alpha} \cap \mathcal{F}^{\alpha} = \emptyset, \ \mathcal{B}^{\alpha} \cap \mathcal{J}^{\alpha} = \emptyset, \ y \ \mathcal{F}^{\alpha} \cap \mathcal{J}^{\alpha} = \emptyset$$

$$\mathcal{B}^{\beta} \cap \mathcal{F}^{\beta} = \emptyset, \ \mathcal{B}^{\beta} \cap \mathcal{J}^{\beta} = \emptyset, \ y \ \mathcal{F}^{\beta} \cap \mathcal{J}^{\beta} = \emptyset$$

since  $card(\mathcal{P}^{\alpha}) = card(\mathcal{P}^{\beta})$ , it is verified that

$$card(\mathcal{J}^{\alpha}) + card(\mathcal{B}^{\alpha}) + card(\mathcal{F}^{\alpha}) = card(\mathcal{J}^{\beta}) + card(\mathcal{B}^{\beta}) + card(\mathcal{F}^{\beta})$$

considering  $card(\mathcal{J}^{\alpha}) = card(\mathcal{J}^{\beta})$ , and the expressions 1 and 2, we know that

$$card(\mathcal{B}^{\alpha}) + k - card(\mathcal{F}^{\beta}) = k - card(\mathcal{B}^{\alpha}) + card(\mathcal{F}^{\beta})$$

$2 * card(\mathcal{B}^{\alpha}) = 2 * card(\mathcal{F}^{\beta})$

$card(\mathcal{B}^{\alpha}) = card(\mathcal{F}^{\beta})$

this demonstrates the first clause of the Proposition.

In a similar procedure, but using the equations 3 and 4, the second clause of the Proposition is proved, that is,

$$card(\mathcal{B}^{\beta}) = card(\mathcal{F}^{\alpha})$$

As it is suggested by the Figure 2, we assume that:

- $\operatorname{card}(\mathcal{B}^{\alpha}) = p^{\alpha}$ .

- $\operatorname{card}(\mathcal{F}^{\alpha}) = q^{\alpha}$ .

- $\operatorname{card}(\mathcal{B}^{\beta}) = p^{\beta}$ .

- $\operatorname{card}(\mathcal{F}^{\beta}) = q^{\beta}$ .

thus from Proposition 1.1, it is possible to conclude that  $p^{\alpha} = q^{\beta}$  and  $q^{\alpha} = p^{\beta}$ .

Accordingly, and in order to use a simpler notation and without loss of accuracy in the final solution, or rigor in the procedure, the following simplifications are assumed:

$$card(\mathcal{B}^{\alpha}) = card(\mathcal{F}^{\beta}) = p.$$

(5)

$$card(\mathcal{B}^{\beta}) = card(\mathcal{F}^{\alpha}) = q.$$

(6)

**Definition 1.8** Let  $C^i \subset \mathcal{U}$  be the configuration of an internal switch i of a T-switch, where i defines the set of ports on the switch i, which are a subset of the ports of the T-switch, where  $i \in \{\alpha, \beta\}$ . Hence,

$$\mathcal{C}^i = \mathcal{B}^i \cup \mathcal{F}^i$$

**Proposition 1.2** The number of elements in  $C^i$  is k, where  $i \in \{\alpha, \beta\}$ . In other words  $card(C^i) = k$ .

**Proof:** The cardinal of  $C^{\alpha}$  is

$$card(\mathcal{C}^{\alpha}) = card(\mathcal{B}^{\alpha}) + card(\mathcal{F}^{\alpha})$$

From the Proposition 1.1, we know that  $\operatorname{card}(\mathcal{B}^{\beta}) = \operatorname{card}(\mathcal{F}^{\alpha})$ . Thus

$$card(\mathcal{C}^{\alpha}) = card(\mathcal{B}^{\alpha}) + card(\mathcal{B}^{\beta})$$

As defined above in Definition 1.7,  $\mathcal{B}^{\alpha}$  and  $\mathcal{B}^{\beta}$  are disjoint sets and  $\mathcal{B} = \mathcal{B}^{\alpha} \cup \mathcal{B}^{\beta}$ . Therefore,  $card(\mathcal{B}) = card(\mathcal{B}^{\alpha}) + card(\mathcal{B}^{\beta})$ . By substituting in the above equation, we get

$$card(\mathcal{C}^{\alpha}) = card(\mathcal{B}) = k$$

Starting from  $\mathcal{C}^{\beta}$  and applying the same process, we will also reach the conclusion that  $card(\mathcal{C}^{\beta}) = k$ .

**Definition 1.9** Let V be the set of all possible configurations of an internal switch i in a T-switch, where  $i \in \{\alpha, \beta\}$ . Hence,

$$\mathcal{V} = \{ \mathcal{C}^i \subset \mathcal{U} \mid card(\mathcal{C}^i) = k \}$$

It is important to note that  $\mathcal{U}$  is a set, while  $\mathcal{V}$  is a set whose members are sets. That is, any configuration  $\mathcal{C}^i$  is contained in  $\mathcal{U}$ , and belongs to  $\mathcal{V}$ . Formally:

$$\mathcal{C}^i \subset \mathcal{U}$$

$\mathcal{C}^i \in \mathcal{V}$

Hereafter, the configuration of an internal switch will be denoted by C, when it does not matter if the switch configuration refers to the switches  $\alpha$  or  $\beta$ . The superscript will be only used when necessary to distinguish between  $\alpha$  and  $\beta$ .

**Definition 1.10** Let  $\mathcal{T}$  be the configuration of T-switch, which is determined by a pair of configurations belonging to  $\mathcal{V}$ . Hence,

$$\mathcal{T} = \{ \mathcal{C}^{\alpha}, \ \mathcal{C}^{\beta} \in \mathcal{V} \mid \mathcal{C}^{\beta} = (\mathcal{C}^{\alpha})^{C} \}$$

**Definition 1.11** Let  $\gamma$  be a pattern of connections that are applied to a T-switch. Then we define  $S^{\gamma}$  as the subset of V, whose configurations minimize the number of connections using the ports  $\mathcal{J}$  of the internal switches. In other words:

$$\mathcal{S}^{\gamma} = \{ \mathcal{C} \in \mathcal{V} \mid \mathcal{C} \text{ minimizes the use of ports} \mathcal{J} \}$$

**Proposition 1.3** Let  $\mathcal{T}$  be a configuration of a T-switch. The configuration  $\mathcal{T}$  is an optimal configuration for a specific pattern of connections  $\gamma$  if the configuration of its internal switches belongs to  $\mathcal{S}^{\gamma}$ . In other words:

If

$$\mathcal{T} = \{\mathcal{C}^{\alpha}, \ \mathcal{C}^{\beta} \mid \mathcal{C}^{\alpha}, \ \mathcal{C}^{\beta} \in \mathcal{S}^{\gamma}\}, \ then \ \mathcal{T} \ is \ optimal$$

**Proof:** The proof is trivial. The configurations belonging to  $S^{\gamma}$  minimize the number of connections that use the internal link. Consequently,  $\mathcal{T}$  is optimal since there are other configurations that minimize the total connections.

The T-MINs are MIN networks built using T-switches. These networks can be both unidirectional and bidirectional. Our study in this report focuses only on the last ones, however the study of the unidirectional are quite similar.

**Definition 1.12** A T-MIN interconnection network is a MIN network in which all the switches are T-switches.

**Definition 1.13** A T-BMIN interconnection network is a BMIN network in which all the switches are T-switches.

#### 4.1 Internal connections of Twin switches

A  $k \times k$  T-switch, like any other same size full-duplex switch allows a set of connections between their ports. In particular, we have

• Forward and backward connections. There are  $k \times k$  possible combinations that imply pass through the T-switch (in forward and backward directions). We denote by  $CC(\langle s, o \rangle)$  (cross connections) the number of different connections between k input ports and k output ports, so  $CC(\langle s, o \rangle) = k^2$ . If necessary to make a difference between forward and backward directions we will denote by  $CC_f(\langle s, o \rangle)$  and  $CC_b(\langle s, o \rangle)$ , respectively. Hence,

$$CC_f(\langle s, o \rangle) = CC_b(\langle s, o \rangle) = k^2$$

• Turnaround connections. Only k ports take part to establish this type of connection. We denote by  $TC(\langle s, o \rangle)$  (turnaround connections) the number of different connections between such ports. It is assumed that there is no turnaround connection between a port and itself. Hence,

$$TC(\langle s, o \rangle) = k(k-1)$$

For the two connection types, considering the internal organization of the T-switch, some of them imply to go across the internal links  $\mathcal{J}$  that interconnect the switches  $\alpha$  and  $\beta$ . We denote by  $CC_I(\langle s,o\rangle)$  the number of paths that go across the  $\langle s,o\rangle$  switch by using the switches  $\alpha$  and  $\beta$ . Similarly, We denote by  $TC_I(\langle s,o\rangle)$  the number of paths that turn around the  $\langle s,o\rangle$  switch by using the switches  $\alpha$  and  $\beta$ . When necessary, we will differentiate the forward from backward direction by  $CC_{If}(\langle s,o\rangle)$  and

$CC_{Ib}(\langle s, o \rangle)$ , respectively. In Figure 2, and taking into account the expressions 5 and 6 it is deduced that:

$$CC_I(\langle s, o \rangle) = p \times p + q \times q = p^2 + (k - p)^2 = 2p^2 + k^2 - 2kp$$

$TC_I(\langle s, o \rangle) = p \times q + q \times p = 2p(k - p) = 2(kp - p^2)$

and also

$$CC_{If}(\langle s, o \rangle) = p \times p + q \times q = p^2 + (k - p)^2 = 2p^2 + k^2 - 2kp$$

$CC_{Ib}(\langle s, o \rangle) = p \times p + q \times q = p^2 + (k - p)^2 = 2p^2 + k^2 - 2kp$

The total number of times that the internal links connecting the internal switches  $\alpha$  and  $\beta$  on a  $\langle s, o \rangle$  T-switch would be used, is denoted by  $C_i(\langle s, o \rangle)$ , and it is obtained from the  $CC_I(\langle s, o \rangle)$  ( $CC_{If}(\langle s, o \rangle)$  and  $CC_{Ib}(\langle s, o \rangle)$  if applicable) and  $TC_I(\langle s, o \rangle)$  in each case are obtained under the initial conditions.

In the previous, we saw the expressions  $CC_I(\langle s, o \rangle)$  and  $TC_I(\langle s, o \rangle)$  that have been obtained considering the isolated T-switch, without taking into account the entire network; nor the paths that are routed by the concrete routing algorithm; nor the characteristics of the traffic that determine the paths. Once all these aspects are considered, it is possible to determine what happens in individual cases and therefore we can get the configuration of all network T-switches to minimize the number of crosses by the internal links <sup>2</sup> that interconnect the switches  $\alpha$  and  $\beta$ .

In such cases, the number of paths that pass through switches can be calculated using these expressions or not (depending on the characteristics of each case), all the paths that pass through or turn on each  $\langle s, o \rangle$  switch, and which of them make it through the switches  $\alpha$  and  $\beta$ .

To obtain these expressions we need to know when a path reaches the switch  $\langle s, o \rangle$ . Considering that is a BMIN network topology of N nodes and n stages, a switch  $\langle s, o \rangle$  will be achieved:

- from a switch located in a previous stage or from one terminal node to reach a later stage. In this case the path goes across the switch. We denote by  $C_f(\langle s, o \rangle)$  (a.k.a. forward crosses) the number of paths that go across the switch  $\langle s, o \rangle$ ,  $0 \le s < n-1$ , in the forward direction. This is true for switches belonging to all stages except the last.

- from a switch located in a later stage to arrive at an previous stage or a terminal node. In this case the path goes across the switch. We denote by  $C_b(\langle s, o \rangle)$  (a.k.a. backward crosses) the number of paths that go across the switch  $\langle s, o \rangle$ ,

<sup>&</sup>lt;sup>2</sup>In what follows, we will also use the term "internal link" to refer to the ports  $\mathcal{J}$  that connect the switches  $\alpha$  and  $\beta$ .

$0 \le s < n-1$ , in the backward direction. This is also true for switches belonging to all stages except the last.

• from a switch located in a previous stage or a terminal node to reach another different switch in the same stage or different terminal node. In this case there is a twist on the switch itself. We denote by  $T(\langle s, o \rangle)$  (a.k.a. turnaround connection) the number of paths that turn around the switch  $\langle s, o \rangle$ . Unlike earlier, this is true in all switches.

Sometimes it will be convenient to consider  $C_f(\langle s, o \rangle)$  and  $C_b(\langle s, o \rangle)$  together. Thus, we also introduce  $C(\langle s, o \rangle)$  (total crosses) as

$$C(\langle s, o \rangle) = C_f(\langle s, o \rangle) + C_b(\langle s, o \rangle)$$

The above expressions are switch-level expressions, but they do not distinguish between individual ports. However, for this study it is necessary to know which connections are established between individual ports and how many times. This information will determine which of them may be made without using the internal switches  $\alpha$  and  $\beta$ .

Therefore, we will also consider counters similar to those introduced above, but at connection level. But we will distinguish among those going in the forward, downward, or turn-around connections. To register the number of occurrences of each event will be used,  $C_f(\langle s, o \rangle, l, l')$ ,  $C_b(\langle s, o \rangle, l, l')$  and  $T(\langle s, o \rangle, l, l')$ , respectively. In short:

- $C_f(\langle s, o \rangle, l, l')$  records the number of times it is used the connection between the ports l and l', with  $0 \le l < k$  and  $k \le l' < 2k$ .

- $C_b(\langle s, o \rangle, l, l')$  records the number of times it is used the connection between the ports l and l', with  $k \leq l < 2k$  and  $0 \leq l' < k$ .

- $T(\langle s, o \rangle, l, l')$  records the number of times it is used the connection between the ports l and l', with  $0 \le l, l' < k$  and  $l \ne l'$ . The sum of the first two are denoted by  $C(\langle s, o \rangle, l, l')$ .

Adding the first two we obtain  $C(\langle s, o \rangle, l, l')$ .

## 5 Applying the Methodology

Notice that although the methodology is general and it can be applied considering different C-switches and interconnection networks, the optimal T-switch configuration depends on the particular network properties. In this case we have considered the following network properties: BMINs k-ary n-tree with N terminals and  $k \times k$  T-switches ( $k \ge 4$ ), DESTRO routing algorithm, and uniform traffic pattern.

Therefore, in order to apply the switch configuration methodology we must specify the network topology, the routing algorithm, and the network load.

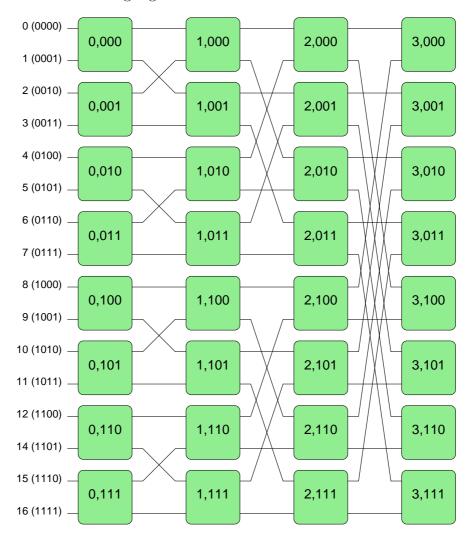

We have chosen the BMIN k-ary n-tree network [DYN03], a subclass of fat-trees which are one of the most common topologies today in the largest supercomputers on the Top500 list. The k-ary n-tree network topology belongs to the family of fat-trees and it is derived from a concrete class of MINs: the k-ary n-butterflies (or k-ary n-flies) [Lei92]. A k-ary n-fly MIN is obtained by applying the  $\beta_i^k$  permutation,  $0 \le i < n$ , to obtain the network-level connection patterns between stages. The k-ary n-tree connect N nodes using  $nk^{n-1}$  switches. Two switches  $\langle s, o_{n-2} \dots o_0 \rangle$  and  $\langle s', o'_{n-2} \dots o'_0 \rangle$  are connected with a link if s' = s + 1 and  $o_i = o'_i \ \forall i \ne s$ . Moreover, there is a link between the switch  $\langle 0, o_{n-2} \dots o_0 \rangle$  and the terminal  $h = h_{n-1} \dots h_0$  if  $o_i = h_{i+1}, 0 \le i < n-1$ .

The routing algorithm is DESTRO [GGG<sup>+</sup>07]. It is a deterministic routing algorithm for fat-trees. It is based on using at each switch the ascending output port given by the destination component of the packet that is being routed corresponding to the switch stage. This routing algorithm is able to evenly balance network traffic and reduce to the minimum the number of paths that share each link, and as a consequence, it reduces network contention.

Uniform traffic pattern is assumed as network workload because it is a common pattern in many studies about interconnection networks.

Under these conditions, we formally demonstrate what is the best configuration of the T-switches. The following three sections correspond to the steps in the methodology.

## 5.1 Networks paths analysis

For a further treatment, it is interesting to know the reachable nodes from a particular BMIN switch. We have distinguished two cases: (1) in the first case we only take into account the topological capabilities of butterfly BMINs; (2) however in the second case, we have additionally considered a routing algorithm. In both cases, we introduce some definitions and derived propositions. Before every definition, we give an example for a sake of clarity.

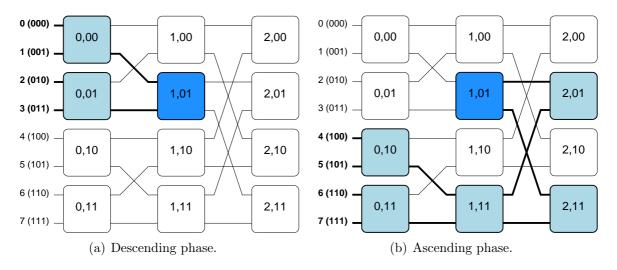

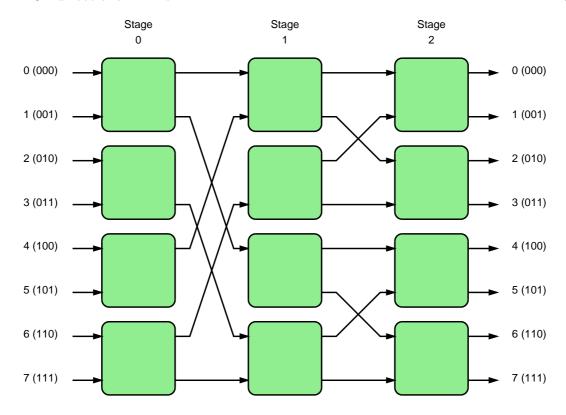

In all the examples, we assume a 2-ary 3-tree BMIN with N=8 nodes, and consider the  $\langle 1,01 \rangle$  (dark blue) as the reference switch. On the other hand, we highlight in light blue the switches in the middle of the reference switch and the reachable nodes.

# 5.1.1 Reachable nodes from a BMIN switch considering the network topology

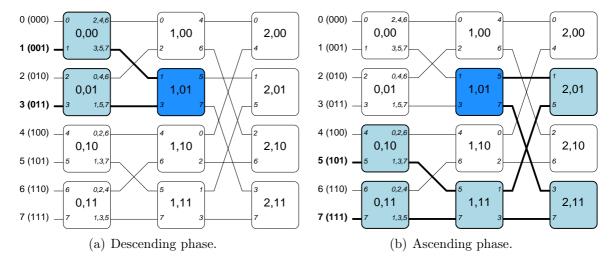

**Example 1.1** Topologically speaking, a path can reach the nodes  $\{0,1,2,3\}$  in the descending phase, and the nodes  $\{4,5,6,7\}$  in the ascending phase, from the  $\langle 1,01\rangle$  switch, as it can be seen in the Figures 3(a) and 3(b), respectively.

Figure 3: Reachable nodes from a switch considering the topology.

**Example 1.2** Topologically speaking, a path can reach the nodes  $\{0,1\}$  in the descending phase by using the output port 0, and the nodes  $\{4,5,6,7\}$  in the ascending phase by using the output port 2, from the  $\langle 1,01 \rangle$  switch, as it can be seen in the figures 4(a) and 4(b), respectively.

In a more formal way, given a k-ary n-tree BMIN network with N nodes, we introduce the following definitions:

**Definition 1.14** Let  $N_b^t(\langle s, o \rangle)$  be the network node set that are topologically reachable from the switch  $\langle s, o \rangle$  by a path in the descending phase, where  $\langle s, o \rangle = \langle s, (o_{n-2} \dots o_0) \rangle$  for  $0 \le s < n$ . Hence

$$N_b^t(\langle s, o \rangle) = \{ (h_{n-1} \dots h_0) : h_i = o_{i-1} \ \forall i \in [s+1, n-1] \}$$

**Definition 1.15** Let  $N_f^t(\langle s, o \rangle)$  be the network node set that are topologically reachable from the switch  $\langle s, o \rangle$  by a path in the ascending phase, where  $\langle s, o \rangle = \langle s, (o_{n-2} \dots o_0) \rangle$  for  $0 \le s < n-1$ . Hence

$$N_f^t(\langle s, o \rangle) = (N_b^t(\langle s, o \rangle))^C = \{ (h_{n-1} \dots h_0) : \exists i \in [s+1, n-1] \mid h_i \neq o_{i-1} \}$$

where C refers to set complement operation.

Figure 4: Reachable nodes through a port from a switch considering the topology.

Similarly, we also define the reachable node set by the output port l in the switch  $\langle s, o \rangle$ .

**Definition 1.16** Let  $N_b^t(\langle s, o \rangle, l)$  be the network node set that are topologically reachable by the output port l from the switch  $\langle s, o \rangle$  by a path in the descending phase, where  $\langle s, o \rangle = \langle s, (o_{n-2} \dots o_0) \rangle$  for  $0 \le s < n$  and  $0 \le l < k$ . Hence

$$N_b^t(\langle s, o \rangle, l) = \{ (h_{n-1} \dots h_0) : h_i = o_{i-1} \ \forall i \in [s+1, n-1] \ y \ h_s = l \}$$

**Definition 1.17** Let  $N_f^t(\langle s, o \rangle, l)$  be the network node set that are topologically reachable by using the output port l from the switch  $\langle s, o \rangle$  by a path in the ascending phase, where  $\langle s, o \rangle = \langle s, (o_{n-2} \dots o_0) \rangle$  for  $0 \le s < n-1$  and  $k \le l < 2k$ . Hence

$$N_f^t(\langle s, o \rangle, l) = \{ (h_{n-1} \dots h_0) : \exists i \in [s+1, n-1] \mid h_i \neq o_{i-1} \}$$

Taking the previous definitions as the starting point, the following propositions can be considered:

**Proposition 1.4** The total number of topologically reachable network nodes from the switch  $\langle s, o \rangle$  by a path in the descending phase is  $D_b^t(\langle s, o \rangle) = k^{s+1}$ .

**Proof:** Every node identifier can be written as a sequence of n digits:

$$(h_{n-1} \dots h_{s+1} h_s h_{s-1} \dots h_0)$$

and according to Definition 1.14, the sequence can be rewritten as:

$$(o_{n-2}\dots o_{s+1}o_sh_sh_{s-1}\dots h_0)$$

that is, the n-1-s most significant digits  $o_{n-2} \dots o_s$  are the same for all the set members. The s+1 remaining digits  $h_s \dots h_0$  may be different and distinguish the set nodes between them. Every  $h_i$  would take values inside the range [0, k], that is, k different values. Therefore, the number of different sequences, or the number of set nodes is  $k^{s+1}$ .

**Proposition 1.5** The total number of topologically reachable network nodes from the switch  $\langle s, o \rangle$  by a path in the ascending phase is  $D_f^t(\langle s, o \rangle) = k^n - k^{s+1}$ .

**Proof:** According to Definition 1.15

$$N_f^t(\langle s, o \rangle) = (N_b^t(\langle s, o \rangle))^C$$

therefore

$$D_f^t(\langle s, o \rangle) = card(N_f^t(\langle s, o \rangle)) = card((N_b^t(\langle s, o \rangle))^C) =$$

$$= card(\mathcal{H}) - card(N_b^t(\langle s, o \rangle)) = N - card(N_b^t(\langle s, o \rangle)) = N - k^{s+1} = k^n - k^{s+1}$$

**Proposition 1.6** The total number of topologically reachable network nodes by using the output port l from the switch  $\langle s, o \rangle$  by a path in the descending phase, where  $0 \le s < n$  and  $0 \le l < k$ , is  $D_b^t(\langle s, o \rangle, l) = k^s$ .

**Proof:** If s > 0, the topologically reachable network nodes by using the output port l from the switch  $\langle s, o \rangle$  by a path in the descending phase are the same as the reachable nodes from the switch  $\langle s - 1, o' \rangle$ , which  $\langle s, o \rangle$  is connected to through its port l, hence

$$D_b^t(\langle s, o \rangle, l) = D_b^t(\langle s - 1, o' \rangle) = k^{(s-1)+1} = k^s$$

If s=0, only one node is connected through the port l, and  $D_b^t(\langle 0,o\rangle,l)=k^s$  is also verified because  $k^0=1$ .

**Proposition 1.7** The total number of topologically reachable network nodes by using the output port l from the switch  $\langle s, o \rangle$  by a path in the ascending phase, where  $0 \le s < n-1$  and  $k \le l < 2k$ , is  $D_f^t(\langle s, o \rangle, l) = k^n - k^{s+1}$ .

**Proof:** According to Definitions 1.15 and 1.17, the sets  $N_f^t(\langle s, o \rangle)$  and  $N_f^t(\langle s, o \rangle, l)$  have the same members. Hence,

$$D_f^t(\langle s, o \rangle, l) = D_f^t(\langle s, o \rangle) = k^n - k^{s+1}$$

# 5.1.2 Reachable nodes from a BMIN switch considering the network topology and the routing algorithm

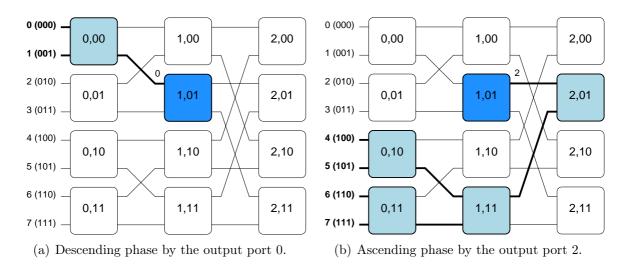

Similar to Section 5.1.1, we also give some examples to understand the following definitions and propositions. The reference switch and the reachable nodes are highlighted in dark and light blue, respectively. Furthermore, every output port is labeled with the reachable network nodes identifier, which are calculated by a routing algorithm likewise the described algorithm in Section A.7.1.

Considering the routing algorithm, we have to take into account that given a switch, i.e.  $\langle 1, 01 \rangle$ , only a concrete destinations are reachable:

**Example 1.3** From switch  $\langle 1,01 \rangle$ , the reachable destinations are  $\{1,3\}$  in the descending phase, and  $\{5,7\}$  in the ascending phase, as it can be seen in the figures 5(a) and 5(b), respectively.

For the reason stated just before starting this example, nodes 0 and 2 are not reachable because the routing algorithm prevents (in every hop) paths for reaching the switch  $\langle 1, 01 \rangle$ .

Figure 5: Reachable nodes from the switch considering the routing algorithm.

**Example 1.4** Let us take the switch  $\langle 1,01 \rangle$  as the reference point. Through the port 0, a path can only reach the node  $\{1\}$  in the descending phase; but through the port 2, the path can only reach the node  $\{5\}$  in the ascending phase. This can be observed in the figures 6(a) and 6(b), respectively.

In a more formal way, given a k-ary n-tree BMIN network with N nodes and considering **DESTRO** (Section A.7.1) as the routing algorithm, R, we introduce the definitions below:

Figure 6: Reachable nodes through a port from a switch considering the routing algorithm.

**Definition 1.18** Let  $N_b^R(\langle s, o \rangle)$  be the reachable network nodes from the switch  $\langle s, o \rangle$  by a path in the descending phase, considering R, where  $\langle s, o \rangle = \langle s, (o_{n-2} \dots o_0) \rangle$ , 0 < s < n. Hence

$$N_h^R(\langle s, o \rangle) = \{ (h_{n-1} \dots h_0) : h_i = o_{i-1} \ \forall i \in [s+1, n-1], h_i = o_i \ \forall i \in [0, s-1] \}$$

**Definition 1.19** Let  $N_f^R(\langle s, o \rangle)$  be the reachable network nodes from the switch  $\langle s, o \rangle$  by a path in the ascending phase, considering R, where  $\langle s, o \rangle = \langle s, (o_{n-2} \dots o_0) \rangle$ ,  $0 \le s < n-1$ . Hence

$$N_f^R(\langle s, o \rangle) = \{ (h_{n-1} \dots h_0) : \exists i \in [s+1, n-1] \mid h_i \neq o_{i-1} \text{ and } h_i = o_i \ \forall i \in [0, s-1] \}$$

Similarly, we also define the reachable node set by the output port l in the switch  $\langle s, o \rangle$ .

**Definition 1.20** Let  $N_b^R(\langle s, o \rangle, l)$  be the reachable network node set by using the output port l from the switch  $\langle s, o \rangle$  by a path in the descending phase, considering R, where  $\langle s, o \rangle = \langle s, (o_{n-2} \dots o_0) \rangle$  with  $0 \le s < n$  and  $0 \le l < k$ . Hence

$$N_b^R(\langle s, o \rangle, l) = \{ (h_{n-1} \dots h_0) : h_i = o_{i-1} \ \forall i \in [s+1, n-1], \ h_s = l, \ and h_i = o_i \ \forall i \in [0, s-1] \}$$

**Definition 1.21** Let  $N_f^R(\langle s, o \rangle, l)$  be the reachable network node set by using the output port l from the switch  $\langle s, o \rangle$  by a path in the ascending phase, considering R, where  $\langle s, o \rangle = \langle s, (o_{n-2} \dots o_0) \rangle$  with  $0 \le s < n-1$  and  $k \le l < 2k$ . Hence

$$N_f^R(\langle s, o \rangle, l) = \{ (h_{n-1} \dots h_0) : \exists i \in [s+1, n-1] \mid h_i \neq o_{i-1}, \text{ and } h_s = l-k, y h_i = o_i \ \forall i \in [0, s-1] \}$$

Taking the previous definitions as the starting point, the following propositions can be considered:

**Proposition 1.8** The number of reachable network nodes from the switch  $\langle s, o \rangle$  by a path in the descending phase, considering R, is  $D_b^R(\langle s, o \rangle) = k$ .

**Proof:** The network node identifier is a sequence of n digits:

$$(h_{n-1} \dots h_{s+1} h_s h_{s-1} \dots h_0)$$

and according to Definition 1.18, the sequence can be rewritten as:

$$(o_{n-2} \dots o_{s+1} o_s h_s o_{s-1} \dots o_0)$$

All the digits are the same as those of the switch  $\langle s, o \rangle$ , with the exception of the digit  $h_s$ . Therefore, the digit  $h_s$  makes the difference of the node identifiers in the set. Since  $h_s$  could take k values  $(0 \le h_s < k)$ , there are k different members belonging to the set  $N_b^R(\langle s, o \rangle)$ , and consequently  $D_b^R(\langle s, o \rangle) = k$ .

**Proposition 1.9** The number of reachable network nodes from the switch  $\langle s, o \rangle$  by a path in the ascending phase, considering R, is  $D_f^R(\langle s, o \rangle) = k^{n-s} - k$ .

**Proof:** Every node identifier is a sequence of n digits with the format below:

$$(h_{n-1} \dots h_{s+2} h_{s+1} h_s h_{s-1} \dots h_0)$$

and according to Definition 1.19, such a sequence can be rewritten as:

$$(h_{n-1} \dots h_{s+2} h_{s+1} h_s o_{s-1} \dots o_0)$$

The Definition 1.19 states the n-s-1 most significant digits,  $h_{n-2} \dots h_s$  provide  $k^{n-s-1}$  different combinations of valid sequences. However, there is only one combination that does not verify the Definition 1.19. Specifically, it is that which has

$h_{n-1} \dots h_{s+1} = o_{n-2} \dots o_s$ . In that way, the number of combinations for the n-s-1 left most significant digits is  $k^{n-s-1}-1$ .

On the other hand, the s least significant digits,  $h_{s-1} \dots h_0$ , are fixed by Definition 1.19.

Finally, the digit  $h_s$  would take one value of k possibilities. Therefore, the number of possible combinations for node identifiers, that is, the members of the set  $N_f^R(\langle s, o \rangle)$  is  $(k^{n-s-1}-1)\times k = k^{n-s}-k$ .

**Proposition 1.10** The number of reachable network nodes by using the output port l from the switch  $\langle s, o \rangle$  by a path in the descending phase, considering R, where  $0 \le l < k$  and  $0 \le s < n$ , is  $D_b^R(\langle s, o \rangle, l) = 1$ .

**Proof:** According to Proposition 1.8, the number of reachable network nodes from the switch  $\langle s, o \rangle$  by a path in the descending phase is k, and because R is balanced, those nodes are uniformly distributed between the k output ports, and therefore

$$D_b^R(\langle s,o\rangle,l) = D_b^R(\langle s,o\rangle)/k = k/k = 1$$

**Proposition 1.11** The number of reachable network nodes through the output port l from the switch  $\langle s, o \rangle$  by a path in the ascending phase, considering R, where  $k \leq l < 2k$  and  $0 \leq s < n-1$  is  $D_f^R(\langle s, o \rangle, l) = k^{n-s-1} - 1$ .

**Proof:** According to Proposition 1.9, the number of reachable nodes from the switch  $\langle s, o \rangle$  by a path in the ascending phase is  $k^{n-s} - k$ , and since R is balanced, those nodes are uniformly distributed between the k output ports, and therefore

$$D_f^R(\langle s,o\rangle,l) = D_f^R(\langle s,o\rangle)/k = (k^{n-s}-k)/k = k^{n-s-1}-1$$

**Proposition 1.12** Given an input port l,  $k \le l < 2k$ , an output port l',  $0 \le l' < k$ , and both belong to a switch  $\langle s, o \rangle$ , where  $\langle s, o \rangle = \langle s, (o_{n-2} \dots o_0) \rangle$  with  $0 \le s < n-1$ , considering R, there exist paths in the descending phase that arrive at  $\langle s, o \rangle$  by l and leave it through l' if and only if l' = l - k is verified.

**Proof:** Let us suppose that a path in the descending phase arrives at the switch  $\langle s, o \rangle$ , and let h' be the destination node of that path. The path would leave the switch through the output port l' in the switch  $\langle s, o \rangle$ .

Figure 7: Associated channel between two adjacent switches.

Since R is the routing algorithm, the Definition 1.20 determines the reachable nodes by a path in the descending phase in  $\langle s, o \rangle$  by using l'. According to Proposition 1.10, such a set has only one member, this is, the destination node h':

$$N_b^R(\langle s, o \rangle, l') = \{ h' \} = \{ (o_{n-2} \dots o_{s+1} o_s l' o_{s-1} \dots o_0) \}$$

Since the path is in the descending phase, it comes from one of the switches placed in the upwards stage  $\langle s', o' \rangle$ , with s' = s + 1. If a path passes through two switches, each one belonging to different stages, both switches are connected by a channel. For example, in the Figure 7, the switches  $\langle s, o \rangle$  and  $\langle s', o' \rangle$  are connected through the ports l and l''. Taking into account the k-ary n-tree topology definition, it is known the switch identifiers verify  $o_i = o'_i \ \forall i \neq s$ , in other words:

$$\langle s', o' \rangle = \langle s+1, (o_{n-2} \dots o_{s+1} o'_s o_{s-1} \dots o_0) \rangle$$

It should be notice all the values that o' can take are known except  $o'_s$ .

On the other hand, the Definition 1.20 specifies the reachable network node set in the descending phase from the switch  $\langle s', o' \rangle$  through the output port l''. Such a set has only one member: the destination node h':

$$N_b^R(\langle s', o' \rangle, l'') = \{h'\} = \{ (o_{n-2} \dots o_{s+1} l'' o'_s o_{s-1} \dots o_0) \}$$

Since the sets  $N_b^R(\langle s, o \rangle, l')$  and  $N_b^R(\langle s', o' \rangle, l'')$  have the same members,  $\{h'\}$ ,

$$N_b^R(\langle s, o \rangle, l') = \{ (o_{n-2} \dots o_{s+1} o_s l' o_{s-1} \dots o_0) \}$$

$$N_b^R(\langle s', o' \rangle, l'') = \{ (o_{n-2} \dots o_{s+1} l'' o'_s o_{s-1} \dots o_0) \}$$

that is checked only if:

$$o'_s = l'$$

$o_s = l''$

Let us analyze the relation between l and l'' with the connection pattern. The pattern was defined in Section A.2 in terms of global ports L and L''. The number of

internal port  $l, k \leq l < 2k$ , is associated with  $L = l_{n-1} \dots l_0$  by the connection pattern as:

$$L = k \times o + (l - k) = k \times (o_{n-2} \dots o_0) + (l - k) = o_{n-2} \dots o_0(l - k)$$

The multiplication of  $o = o_{n-2} \dots o_0$  (in base k) by k is calculated by shifting  $o = o_{n-2} \dots o_0$  left one position, and assigning the digit  $o_0 = 0$ . Then the addition operation sets the digit  $o_0$  to l - k ( $0 \le l - k < k$ ).

Similarly, the global port number  $L'' = l''_{n-1} \dots l''_0$  is related with the internal port l'',  $0 \le l'' < k$ , by the expression below:

$$L'' = k \times o' + l'' = k \times (o'_{n-2} \dots o'_0) + l'' = o'_{n-2} \dots o'_0 l''$$

Then again, the butterfly permutation associates the ports L and L'' as follows:

$$\beta_{s+1}^k(L) = L''$$

$$\beta_{s+1}^k(o_{n-2}\dots o_{s+1}o_s o_{s-1}\dots o_0(l-k)) = o'_{n-2}\dots o'_{s+1}o'_s o'_{s-1}\dots o'_0l''$$

taking into account that  $o'_s = l'$  and  $l'' = o_s$ , it is obtained in L''

$$\beta_{s+1}^k(o_{n-2}\dots o_{s+1}o_so_{s-1}\dots o_0(l-k)) = o'_{n-2}\dots o'_{s+1}l'o'_{s-1}\dots o'_0o_s$$

(7)

how the switches  $\langle s, o \rangle$  and  $\langle s', o' \rangle$  are related

$$\langle s', o' \rangle = \langle s+1, (o_{n-2} \dots o_{s+1} o'_s o_{s-1} \dots o_0) \rangle$$

and it can be substituted in the Expression 7, remaining then

$$\beta_{s+1}^k(o_{n-2}\dots o_{s+1}o_so_{s-1}\dots o_0(l-k)) = o_{n-2}\dots o_{s+1}l'o_{s-1}\dots o_0o_s$$

at long last, the butterfly permutation is applied

$$o_{n-2} \dots o_{s+1}(l-k)o_{s-1} \dots o_0 o_s = o_{n-2} \dots o_{s+1}l'o_{s-1} \dots o_0 o_s$$

(8)

The equality 8 is verified when l' = l - k.

It should be remembered that the purpose of this first step is to know the connections required in each T-switch that is to obtain  $C_f(\langle s, o \rangle)$ ,  $T(\langle s, o \rangle)$  and  $C_b(\langle s, o \rangle)$  both at switch and port level.

Firstly, the generated paths with uniform traffic pattern are studied. This traffic pattern generates  $N^2-N$  different paths between N terminals in the network. Since we are assuming a deterministic routing algorithm, there is a unique path between every pair of terminals. Moreover, as the routing algorithm is load-balanced, the paths in the ascending, turnaround and descending phase are uniformly distributed among all the switches at the same stage.

Then, the number of paths passing through the switch  $\langle s, o \rangle$  in the ascending, turnaround and descending phases,  $0 \leq s < n$ , are determined. In order to get a more clear and simple treatment, we will avoid continually repeating the starting conditions in every definition and proposition.

#### 5.1.3 Ascending phase of the paths

Some propositions related to the paths passing through the switch  $\langle s, o \rangle$  in the ascending phase,  $0 \le s < n$ , are described below.

**Proposition 1.13** Given the ports l and l' of the switch  $\langle s, o \rangle$ ,  $0 \le s < n-1$ ,  $0 \le l < k$  and  $k \le l' < 2k$ , there are  $k^{n-1} - k^s$  paths passing through  $\langle s, o \rangle$  in the ascending phase by using l and l'.

**Proof:** A path passes through the switch  $\langle s, o \rangle$  in the ascending phase by using the ports l and l' if the source node, h, belongs to the set  $N_b^t(\langle s, o \rangle, l)$ , the destination node, h', belongs to the set  $N_f^R(\langle s, o \rangle, l')$ . Therefore, the total number of paths that pass through  $\langle s, o \rangle$  in the ascending phase by using l and l' is equal to the number of source—destination pairs of nodes obtained from these sets.

$$C_f(\langle s, o \rangle, l, l') = card(N_b^t(\langle s, o \rangle, l)) \times card(N_f^R(\langle s, o \rangle, l')) =$$

$$= D_b^t(\langle s, o \rangle, l) \times D_f^R(\langle s, o \rangle, l') = k^s \times (k^{n-s-1} - 1) = k^{n-1} - k^s$$

that is

$$C_f(\langle s, o \rangle, l, l') = k^{n-1} - k^s$$

**Proposition 1.14** The number of paths in ascending phase passing through the switch  $\langle s, o \rangle$ ,  $0 \le s < n-1$ , is  $k^{n+1} - k^{s+2}$ .

**Proof:** The total number of paths in the ascending phase passing through the switch  $\langle s, o \rangle$  is given by the multiplication of the number of paths that use l and l' ( $0 \le l < k$  and  $k \le l' < 2k$ ) by the number of pairs (l, l').

$$C_f(\langle s, o \rangle) = C_f(\langle s, o \rangle, l, l') \times k^2 = (k^{n-1} - k^s) \times k^2 = k^{n+1} - k^{s+2}$$

that is

$$C_f(\langle s, o \rangle) = k^{n+1} - k^{s+2}$$

**Proposition 1.15** There is no path passing through, in the ascending phase, the switches of the last stage. Hence,

$$C_f(\langle n-1, o \rangle) = C_f(\langle n-1, o \rangle, l, l') = 0$$

**Proof:** By the definition of the BMIN topology, there are no forward connections in the switches of the last stage.  $\Box$

#### 5.1.4 Turnaround phase of the paths

Some propositions related to the paths passing through the switch  $\langle s, o \rangle$  in the turnaround phase,  $0 \le s < n$ , are described below.

**Proposition 1.16** Given the ports l and l' of the switch  $\langle s, o \rangle$ , where  $0 \leq s < n$ ,  $0 \leq l, l' < k$  and  $l \neq l'$ , there are  $k^s$  paths passing through  $\langle s, o \rangle$  in the turnaround phase by using l and l'.

**Proof:** A path is turned around in the switch  $\langle s, o \rangle$  by the ports l and l' if the source node, h, belongs to the set  $N_b^t(\langle s, o \rangle, l)$  and the destination node, h', belongs to the set  $N_b^R(\langle s, o \rangle, l')$ . Therefore, the total number of paths passing through the switch  $\langle s, o \rangle$  in the turnaround phase by using l and l' is equal to number of source–destination node pairs obtained from these sets.

$$T(\langle s, o \rangle, l, l') = card(N_b^t(\langle s, o \rangle, l)) \times card(N_b^R(\langle s, o \rangle, l')) =$$

$$= D_b^t(\langle s, o \rangle, l) \times D_b^R(\langle s, o \rangle, l') = k^s \times 1 = k^s$$

that is

$$T(\langle s,o\rangle,l,l')=k^s$$

**Proposition 1.17** The number of paths that turn around in the switch  $\langle s, o \rangle$ ,  $0 \le s < n$ , is  $(k-1)k^{s+1}$ .

**Proof:** The total number of paths passing through the switch  $\langle s, o \rangle$  in the turnaround phase is obtained by the multiplication of the number of paths that use l and l'  $(0 \le l < k \text{ and } k \le l' < 2k)$  by the number of pairs (l,l'). The first element of the multiplication is obtained by the Proposition 1.16 and the second one, taking into account that no path turns in a switch using the same port as input and output.

$$T(\langle s, o \rangle) = T(\langle s, o \rangle, l, l') \times k(k-1) = k^s \times k(k-1) = (k-1)k^{s+1}$$

that is

$$T(\langle s, o \rangle) = (k-1)k^{s+1}$$

#### 5.1.5 Descending phase of the paths

Some propositions related to the paths passing through the switch  $\langle s, o \rangle$  in the descending phase,  $0 \le s < n$ , are described below.

**Proposition 1.18** There is no path passing through, in the descending phase, the switches of the last stage. Hence,

$$C_b(\langle n-1,o\rangle) = C_b(\langle n-1,o\rangle,l,l') = 0$$

**Proof:** By the definition of the BMIN topology, there are no backward connections in the switches of the last stage.  $\Box$

**Proposition 1.19** Given the ports l and l' of the switch  $\langle s, o \rangle$ , where  $0 \le s < n - 1$ ,  $k \le l < 2k$  and  $0 \le l' < k$ , at the most there exist  $k^n - k^{s+1}$  paths passing through  $\langle s, o \rangle$  in the descending phase by using l and l'.

**Proof:** A path goes through the switch  $\langle s, o \rangle$  in the descending phase by using the ports l and l' if the source node, h, belongs to the set  $N_f^t(\langle s, o \rangle, l)$  and the destination node, h', belongs to the set  $N_b^R(\langle s, o \rangle, l')$ . Therefore, the total number of paths passing through  $\langle s, o \rangle$  in the descending phase by using l and l' is obtained from the number of source–destination node pairs obtained from these sets.

$$C_b(\langle s, o \rangle, l, l') = card(N_f^t(\langle s, o \rangle, l)) \times card(N_b^R(\langle s, o \rangle, l')) =$$

$$= D_f^t(\langle s, o \rangle, l) \times D_b^R(\langle s, o \rangle, l') = (k^n - k^{s+1}) \times 1 = k^n - k^{s+1}$$

**Proposition 1.20** Given the ports l and l' of the switch  $\langle s, o \rangle$ , where  $0 \le s < n - 1$ ,  $k \le l < 2k$  and  $0 \le l' < k$ , there are  $k^n - k^{s+1}$  paths in the descending phase between l and l', if and only if l' = l - k.

**Proof:** According to Proposition 1.19, at the most there are  $k^n - k^{s+1}$  paths in the descending phase using the input port l and the output port l'. Similarly, according to Proposition 1.12 a path passes through  $\langle s, o \rangle$  in the descending phase by using l and l' if l' = l - k is satisfied, and therefore

$$C_b(\langle s, o \rangle, l, l') = \begin{cases} k^n - k^{s+1}, & \text{if and only if } l' = l - k \\ 0, & \text{otherwise} \end{cases}$$

**Proposition 1.21** The number of paths passing through the switch  $\langle s, o \rangle$ ,  $0 \le s < n-1$ , in the descending phase, is  $k^{n+1} - k^{s+2}$ .

**Proof:** The total number of paths passing through the switch  $\langle s, o \rangle$  in the descending phase is obtained from the multiplication of the number of paths that pass through  $\langle s, o \rangle$  by using l and l' ( $0 \le l' < k$  and  $k \le l < 2k$ ) by the number of pairs (l, l'). Such pairs of ports satisfy l' = l - k, in other words, k.

$$C_b(\langle s, o \rangle, l, l') = C_b(\langle s, o \rangle, l, l') \times k = (k^n - k^{s+1}) \times k = k^{n+1} - k^{s+2}$$

that is

$$C_b(\langle s, o \rangle) = k^{n+1} - k^{s+2}$$

To sum up, Table 1 outlines the expressions obtained in the previous propositions.

Table 1: Number of paths passing through the switch  $\langle s, o \rangle$  in the ascending, turnaround and descending phases under uniform traffic.

d and descending phases under uniform traffic.

$$C_f(\langle s,o\rangle) = \begin{cases} k^{n+1} - k^{s+2}, & \text{if } s \in [0, n-2] \\ 0, & \text{if } s = n-1 \end{cases}$$

$$T(\langle s,o\rangle) = (k-1)k^{s+1}$$

$$C_b(\langle s,o\rangle) = \begin{cases} k^{n+1} - k^{s+2}, & \text{if } s \in [0, n-2] \\ 0, & \text{if } s = n-1 \end{cases}$$

$$C(\langle s,o\rangle) = \begin{cases} 2(k^{n+1} - k^{s+2}), & \text{if } s \in [0, n-2] \\ 0, & \text{if } s = n-1 \end{cases}$$

$$C_f(\langle s,o\rangle,l,l') = \begin{cases} k^{n-1} - k^s, & \text{if } s \in [0, n-2] \\ 0, & \text{otherwise} \end{cases}$$

$$T(\langle s,o\rangle,l,l') = k^s$$

$$C_b(\langle s,o\rangle,l,l') = k^s$$

$$C_b(\langle s,o\rangle,l,l') = \begin{cases} k^n - k^{s+1}, & \text{if } s \in [0, n-2] \text{ and } l' = l-k \\ 0, & \text{otherwise} \end{cases}$$

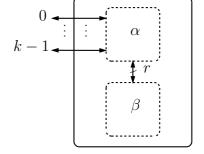

#### 5.2 Switch Classification

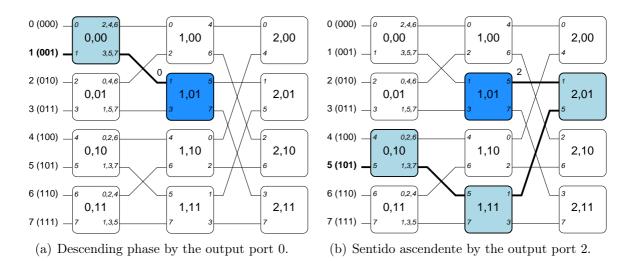

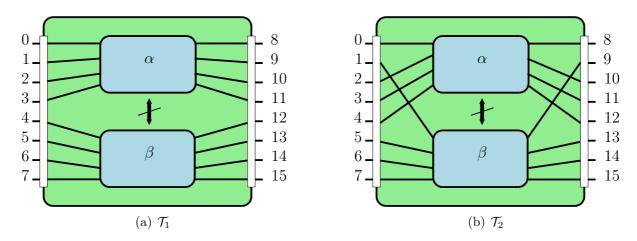

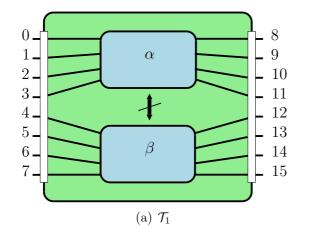

According to the expressions in Table 1, when the network topology is a N end nodes k-ary n-tree T-BMIN, the generated traffic is based on the uniform traffic pattern and the paths are determined by the routing algorithm defined in Section A.7.1, two types of switches are identified according to the connections required in the switches:

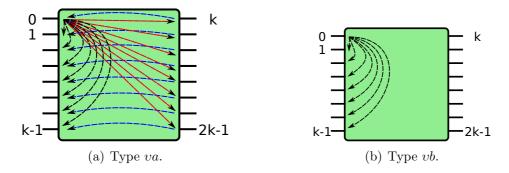

**Type** va Switches establishing forward, turnaround and backward connections belong to this type. The number of paths passing through a switch of this type are obtained by Propositions 1.14, 1.17 and 1.21. Similarly, the number of

connections are determined by Propositions 1.13, 1.16, 1.19 and 1.20. All the switches in the BMIN are Type va, except those placed in the last stage.

**Type** vb Switches that only establish backward connections are Type vb switches according to Propositions 1.15, 1.17 and 1.18. The number of paths passing through one of these switches is determined by Proposition 1.17, and the number of required turnaround connections are obtained by the Proposition 1.16. The switches in the last stage are Type B.

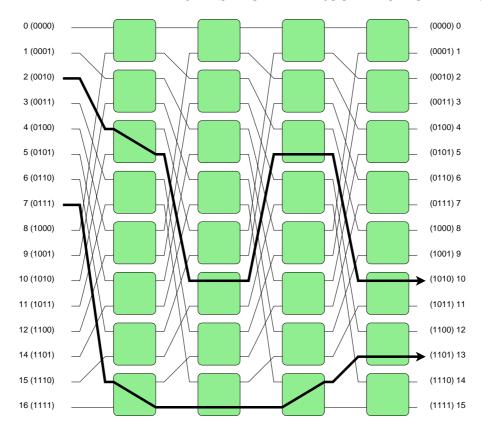

When the paths are uniformly distributed between the ports of the switch, it is not helpful to provide a diagram with all the generated paths as it is done in the previous sections. The Figure 8 shows only the paths passing through the switch by using the input port zero in the ascending and turnaround phases. The remaining paths, whose input port is not equal to zero, have not been included for the sake of clarity. Moreover, the paths in the descending phase are independent from the other phases.

Figure 8(a) shows a Type va switch diagram, where it is shown the paths in the ascending, turnaround and descending phase in red, black and blue color, respectively.

Switches belonging to Type vb only have turnaround connections printed with black color. Figure 8(b) includes the paths from input port zero. The remaining paths from port 1 to k-1 are not drawn for clarity.

Figure 8: Connections required for each type of switch.

## 5.3 Switch Configuration

To apply the third step of the methodology and to find out the most adequate T-switch configuration for each type of switches, we decompose this step in turn in other two substeps:

a) For each type of network switch, and from the number of paths that use of the internal link, and the required connections by these paths in the switch, we will obtain separately the set of optimal configurations for each type of path (i.e. forward, turn-around and backward).

b) For each type of network switch, the optimal set of configurations, from the sets of optimal configurations previously obtained for each type of path, is obtained. In other words, the resulting set is that describes how to provide a 2k-port switch  $\langle s, o \rangle$  from two k-ports internal switches  $\alpha$  and  $\beta$ .

This approach was chosen primarily for two reasons:

- a) It is easier to address several simpler subproblems, from which the global solution can be derived (e.g., divide and conquer strategy) rather than to address the entire problem.

- b) It can be done separately because the behavior of each case is independent of others. The cause because a connection uses or not the internal link only depends on T-switch configuration and is independent of the links to be used by other connections. Therefore, if a configuration minimizes separately the use of the internal link to both forward and backward connections, it also minimizes if we consider both types of connections at a time.

In short, the ultimate goal will be to calculate the set  $S^{\gamma}$  when under a concrete traffic pattern  $\gamma$ .

For the sake of notation and clarity, and different types of connections will be analyzed, we denote by using a superscript in S the link pattern applied, depending on the type of switch to be analyzed. We will use a subscript for indicating the path direction: b (backward), t (turn-around), f (forward), or a combination of them. When hidden, we would assume all the connections in the switch. For example,  $S_b^{\pi a}$  refers to the set of optimal T-switch configurations of type a under uniform traffic pattern(v) and taken into account only the backward connections.

#### 5.3.1 Type va configuration of switch

According to such a methodology, we first obtain the optimal configurations to forward, turnaround and backward connections. In this case, the forward and turnaround connections are considered together, and then we consider separately the backward connections. Finally, we reason about optimal T-switch configurations taking into account all the connections.

# 5.3.1.1 Optimal switch configuration to forward and turnaround connections

**Proposition 1.22** Let  $S_{ft}^{va}$  be the set of configurations that minimize the use of the internal link in a T-switch of type va, considering the forward and turn-around connections, then

$$S_{ft}^{va} = \{ C \in V \mid card(B) = card(F) = k/2 \}$$

and there exist  $\frac{1}{2}k^{n+1}$  connections that use the internal link.

**Proof:** Given a port l,  $0 \le l < k$ , the same number of forward connections are established with each port l',  $k \le l' < 2K$ , and also the same number of turnaround connections with each port l'',  $0 \le l'' < k$  and  $l \ne l''$ . That is, every port l behave identically with independence of the switch.

Therefore, to obtain optimal configurations, it is not necessary to know what specific port is connected to a particular internal switch. It is enough to simply calculate how many upwards and downwards ports are connected to each internal switch. And this is the same as finding the optimal value of p.

However, this reasoning would not be useful if turnaround and forward connections are treated separately: the best configuration for turnaround connections (p=k), is the worst for forward connections, and vice versa. So, we treat both cases together to calculate the value of p that minimizes the number of paths passing through the internal link, considering the two types of connections.

To obtain p, we firstly calculate how many connections use the internal link that interconnects switches  $\alpha$  and  $\beta$ . The resultant expression is dependent on p. Then we apply a mathematical procedure to know which value of p minimizes such as expression.

To know how many paths cross the internal link between  $\alpha$  and  $\beta$  is used,  $C_i$  (Section 4.1), we must take into account the needed connections for any T-switch under uniform traffic, and the internal structure of the T-switch.

Under uniform traffic, it has been shown that paths in the forward and turnaround phases require at least one connection between any pair of ports l and l',  $0 \le l < k$  and  $k \le l' < 2K$ , that is, a total of  $k^2$  and  $k^2 - k$  connections, respectively.

Under these conditions, that is, considering the  $k^2$  possible forward connections in a switch, an expression for  $CC_{If}(\langle s,o\rangle)$  was obtained (Section 4.1), which indicates the number of these connections that use the internal link connecting switches  $\alpha$  and  $\beta$ . In the same way, and considering the  $k^2 - k$  possible turnaround connections in the switch, an expression for  $TC_I(\langle s,o\rangle)$  was obtained, which indicates the number of these connections also involving the use of the internal link connecting switches  $\alpha$  and  $\beta$ .

Therefore, to obtain the contribution to  $C_I(\langle s, o \rangle)$  of the forward and turnaround connections we properly combine the values indicated above for  $CC_{If}(\langle s, o \rangle)$  and  $TC_I(\langle s, o \rangle)$  with  $C_f(\langle s, o \rangle)$  and  $T(\langle s, o \rangle)$ , respectively.

With all the above, the value of  $C_I(\langle s, o \rangle)$  is determined as follows:

$$C_{I}(\langle s, o \rangle) = \frac{C_{f}(\langle s, o \rangle) \times CC_{If}(\langle s, o \rangle)}{k^{2}} + \frac{T(\langle s, o \rangle) \times TC_{I}(\langle s, o \rangle)}{k^{2} - k} =$$

$$= (k^{n-1} - k^{s}) \times (2p^{2} + k^{2} - 2kp) + k^{s} \times 2(kp - p^{2}) =$$

$$= 2p^{2}k^{n-1} - 2p^{2}k^{s} + k^{n+1} - k^{s+2} - 2pk^{n} + 2pk^{s+1} +$$

$$+ 2pk^{s+1} - 2p^{2}k^{s} =$$

$$= 2p^{2}k^{n-1} - 4p^{2}k^{s} + k^{n+1} - k^{s+2} - 2pk^{n} + 4pk^{s+1}$$

To find out the p value that minimizes  $C_I(\langle s, o \rangle)$ , it is required to determine the derivative of  $C_I(\langle s, o \rangle)$  with respect to p.

$$C_I'(\langle s, o \rangle) = \frac{\partial}{\partial p} C_I(\langle s, o \rangle) = 4pk^{n-1} - 8pk^s - 2k^n + 4k^{s+1}$$

The derivative is equal to zero,  $C'_I(\langle s, o \rangle) = 0$ , to calculate the maximum or minimum points.

$$C'_{I}(\langle s, o \rangle) = 0$$

$$4pk^{n-1} - 8pk^{s} - 2k^{n} + 4k^{s+1} = 0$$

$$4pk^{n-1} - 8pk^{s} = 2k^{n} - 4k^{s+1}$$

$$p(4k^{n-1} - 8k^{s}) = 2k^{n} - 4k^{s+1}$$

$$p = \frac{2k^{n} - 4k^{s+1}}{4k^{n-1} - 8k^{s}}$$

As  $0 \le s < n-1$ , the expression can be simplified by removing the common factor  $k^s$

$$p = \frac{k^s(2k^{n-s} - 4k)}{k^s(4k^{n-s-1} - 8)} = \frac{2k^{n-s} - 4k}{4k^{n-s-1} - 8} = \frac{k(2k^{n-s-1} - 4)}{2(2k^{n-s-1} - 4)} = \frac{k}{2}$$